|

Elementi in grado di mantenere memoria, utilizzati nella realizzazione di reti sequenziali. Da un punto di vista energetico presenta due stati stabili (bistabile), ad ognuno dei quali si attribuisce valore 0 oppure 1. Ci sono diversi tipi di bistabili:

Latch S-R

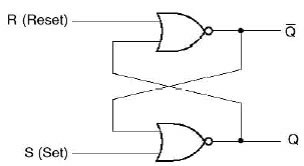

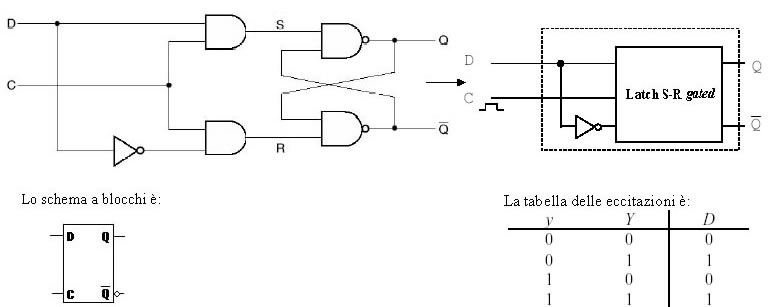

Una delle realizzazioni circuitalmente meno onerose di un bistabile è il latch

(lucchetto) di tipo S-R (Set-Reset) costituito da due porte

NOR retroazionate.

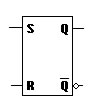

Lo schema a blocchi è:

Viene utilizzato come blocco base per realizzare tutti gli

altri bistabili. Il nome SR di tale latch deriva dal fatto di presentare un

ingresso di eccitazione S (set) e uno di azzeramento R (reset). Questa struttura

permette di memorizzare un valore e cambiarlo.

Si dice che il latch è nello

stato di set se Q=1

Si dice che il latch è nello stato di reset se Q=0

Partendo da ingresso (R,S)=(0,0), l'applicazione di 1 all'ingresso S porta il

latch allo stato di set. L'input S deve essere riportato a 0 prima di cambiare

R al valore di 1, altrimenti si raggiungerebbe lo stato indefinito. Applicando

1 ad R , quando S = 0, si porta il latch nello stato di reset. Quando si applica

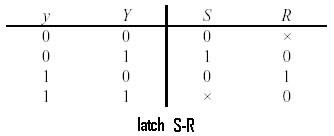

(R,S)=(0,0) si mantiene lo stato precedente. Possiamo sintetizzare quanto detto

in una tabella simile a quella di verità, chiamata tabella di eccitazione

dei bistabili:

Questa tabella ci dice partendo da un certo stato presente y (Q "prima") per raggiungere un certo stato prossimo Y (Q "dopo"), quale/i configurazione/i di ingresso devo utilizzare. Si noti che tale rete è una memoria perché mantiene lo stato precedente a meno che non venga applicato un opportuno segnale di set o reset. Qualsiasi variazione degli ingressi si riflette immediatamente in uscita; il bistabile può quindi essere definito trasparente (transparent latch).

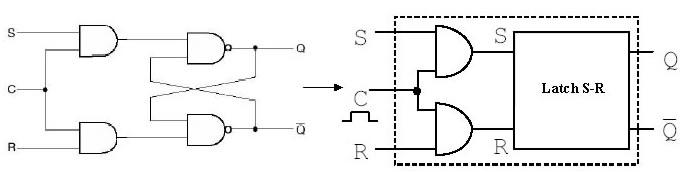

Latch S-R gated

Bistabile nel quale esiste

un ingresso di controllo C che abilita la risposta del latch ai segnali di

ingresso S e R. Si ottiene dal latch S-R inserendo due porte AND prima degli

ingressi S e R, in modo che tali ingressi vengano attivati solo se il segnale

di controllo C collegato a uno dei due ingressi di entrambe le porte AND vale

1.

Lo schema a blocchi è:

La tabella delle eccitazioni quando il segnale di controllo

è attivo è la stessa del Latch S-R.

Qualsiasi variazione di S e/o R mentre

C è attivo si riflette immediatamente sulle uscite, pertanto la trasparenza

viene mantenuta.

Latch D (Delay)

Bistabile nel quale il valore presente all'ingresso D viene riportato all'uscita

Q quando il segnale di controllo C è attivo. In tal caso, si parte da un

latch S-R gated, e si collega l'ingresso D diritto al segnale S e negato

al segnale R. Anche in questo caso è mantenuta la trasparenza:

Si noti che lo stato prossimo Y è uguale all'ingresso D.

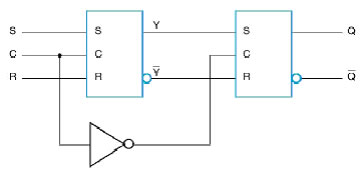

Esistono anche bistabili che non hanno la proprietà della trasparenza; tali bistabili denominati flip-flop sono in grado di variare le proprie uscite solo in risposta a un segnale di controllo (o di clock). Mediante l'adozione del segnale di clock si possono infatti realizzare dei sistemi complessi adeguando tutto il circuito all'elemento più lento ed evitando in tal modo cattivi funzionamenti dovuti proprio alle differenze di velocità dei vari dispositivi. A questo scopo i latches possono essere connessi tra loro ottenendo cosi una configurazione detta Master-Slave (padrone e servitore). Se l'ingresso al bistabile viene considerato solo quando il clock varia da 0 ad 1 e lo stato può cambiare solo in corrispondenza di tale transizione (abilitazione sul fronte di salita del clock) si parla di positive edge triggered, in caso contrario, cioè quando l'abilitazione avviene sul fronte di discesa si parla di negative edge triggered. Noi analizzeremo esempi di Flip Flop positive edge triggered:

Il bistabile di sinistra si dice Master quello di destra si dice Slave. Come si vede il clock è connesso direttamente all'ingresso di controllo del Master e tramite un inverter a quello dello Slave. Il Master commuta sul livello alto dell'impulso, lo Slave su quello basso. Quindi se il Clock=1 il MASTER cambia stato e lo SLAVE conserva l'output precedente, cioè è insensibile ai valori in arrivo, nel momento in cui C=0 è lo SLAVE che cambia stato ed accetta i valori in arrivo. Il vantaggio è che eventuali cambiamenti dell'ingresso dopo la transizione 0 ->1 sono quindi ignorati dal circuito. La tabella delle eccitazioni del bistabile è la stessa del latch S-R. Lo schema a blocchi è:

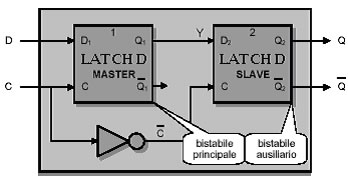

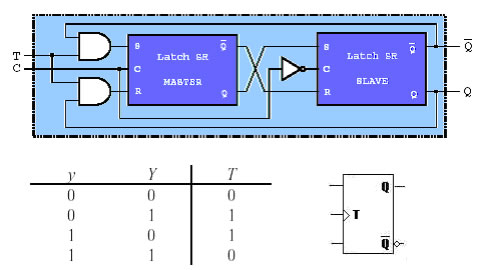

FLIP FLOP D (MASTER SLAVE)

Analogamente

al precedente bistabile questo è costituito da due latch di tipo D in

cascata, l'uscita Q del primo è collegata all'ingresso D del secondo.

In questo modo il valore presente all'ingresso D viene campionato nel

Master sul fronte di salita di C, mentre sul fronte di discesa di C lo

Slave assesta la propria uscita in base a tale valore.

La tabella delle eccitazioni di tale bistabile è la stessa del latch D. Lo schema a blocchi è:

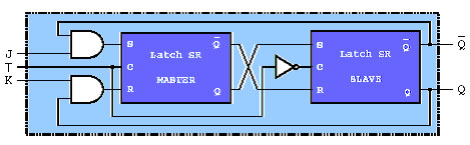

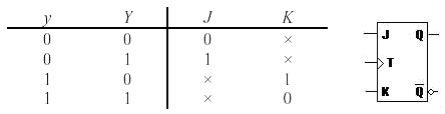

FLIP FLOP J-K (MASTER SLAVE)

Questo bistabile garantisce lo stesso funzionamento di un flip

flop S-R Master Slave, del quale è ben più diffuso. In tale flip flop,

l'ingresso J gioca il ruolo di S, l'ingresso K quello di R e T quello

di C, con l'ulteriore vantaggio di consentire la presenza di due 1 simultanei

sugli ingressi J e K. In tale situazione, il flip flop commuta (toggle)

la propria uscita, complementandola rispetto al valore precedente.

La tabella delle eccitazioni e lo schema a blocchi sono:

FLIP FLOP T (MASTER SLAVE)

Bistabile che commuta la propria uscita ad ogni attivazione del segnale

di sincronismo C:

Tutto quanto riportato in questa pagina è a puro scopo informativo personale. Se non ti trovi in accordo con quanto riportato nella pagina, vuoi fare delle precisazioni, vuoi fare delle aggiunte o hai delle proposte e dei consigli da dare, puoi farlo mandando un email. Ogni indicazione è fondamentale per la continua crescita del sito.